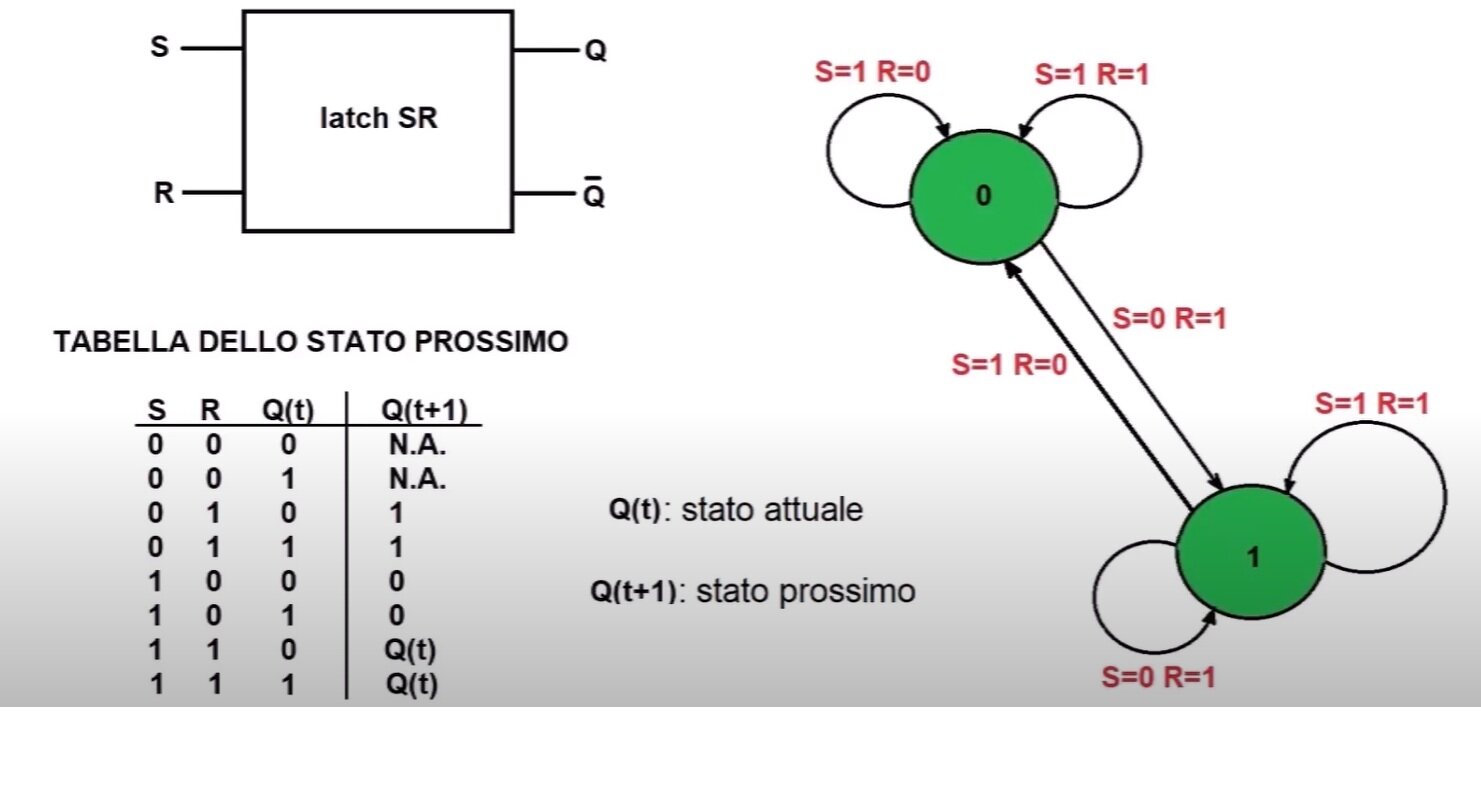

(la videolezione) Il latch Set-Reset (SR) è uno dei circuiti logici fondamentali in elettronica digitale: semplice nella struttura, ma cruciale per il funzionamento di sistemi di memoria.

Il latch SR è un dispositivo bistabile, cioè possiede due stati stabili: uno rappresenta il livello logico alto (1), l’altro quello basso (0). La sua funzione principale è “ricordare” uno stato logico finché non viene fornito un nuovo comando, agendo quindi come una piccola cella di memoria.

Set imposta lo stato a 1.

Reset lo riporta a 0.

Quando entrambi gli ingressi sono a zero, il latch mantiene lo stato precedente (non cambia, rimane “latchato”). Ma se Set è a 1 e Reset a 0, il latch viene impostato; se è il contrario, viene resettato. C’è però una condizione particolare che crea ambiguità: quando sia Set che Reset sono attivi contemporaneamente. In questo caso, il comportamento può essere indefinito e non deterministico.

Nel mondo reale, questo tipo di latch è impiegato come base per circuiti più complessi come i flip-flop, che si sincronizzano con il clock di sistema e sono usati per registri, contatori e memorie. Il latch SR, infatti, è il primo passo verso la logica sequenziale, laddove i circuiti non rispondono solo all’input attuale, ma anche alla loro “storia”. La rete può essere facilmente realizzata con due porte NAND oppure con due NOR. Nella videolezione si discute del latch SR con porte NAND e del suo collaudo in laboratorio.

.png)